Triple Buffering

(Diagram: Uniforms Buffer with Uniforms 1 / 2 / 3, showing CPU writing, data in transit, and GPU reading)

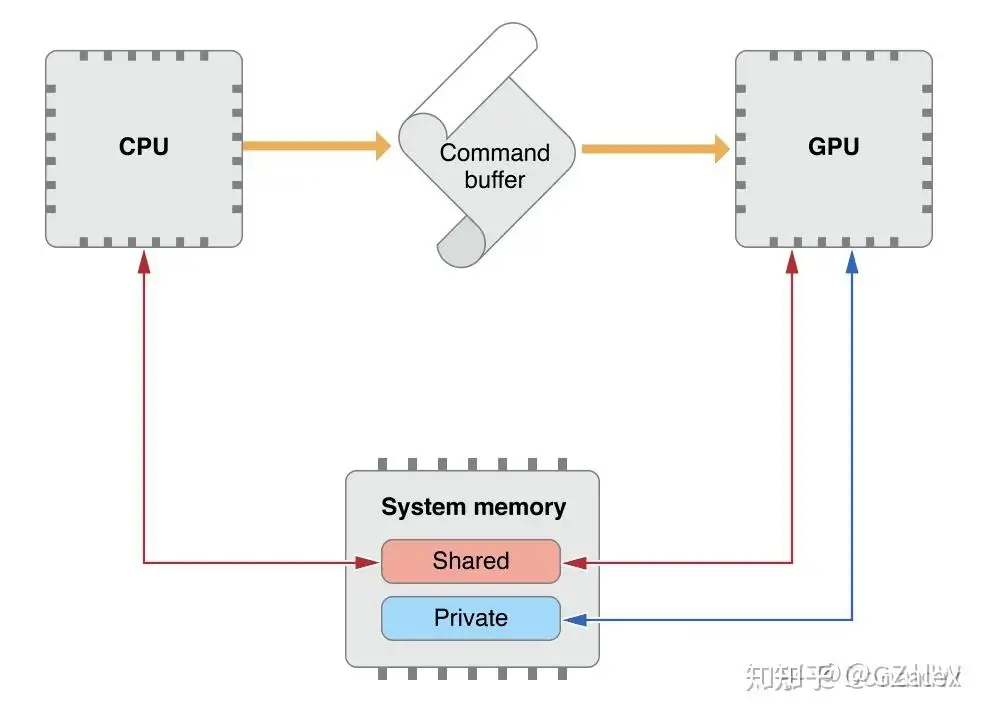

This diagram demonstrates the use of triple buffering for shared memory between the CPU and GPU, especially as a solution to memory access synchronization and performance optimization.

Main Content Explanation

1. Concept of Triple Buffering

- The diagram shows a Uniforms Buffer (a buffer shared by the CPU and GPU) used to store variable data.

- The triple buffering technique uses three buffers to avoid conflicts when the CPU and GPU access the same memory region simultaneously.

- Specifically, the CPU and GPU operate on different buffers, ensuring they do not interfere with each other and thus improving overall performance.

2. CPU Writing Process

- Write Uniforms 1, Write Uniforms 2, Write Uniforms 3

The CPU writes data into different buffers in sequence. - While the CPU writes to one buffer, the GPU can read from another buffer.

- This allows the CPU to continue writing without being blocked by the GPU’s read operations.

3. GPU Reading Process

- Read Uniforms 1, Read Uniforms 2, Read Uniforms 3

The GPU reads data from the Uniforms Buffer. - When the CPU is writing to one buffer, the GPU can read data from another buffer.

- Through this approach, the GPU avoids waiting for the CPU to finish writing and can instead use data from a previously completed buffer.

4. Avoiding Synchronization Issues

- Without triple buffering, the CPU and GPU may access the same data simultaneously, leading to memory conflicts.

For example, the GPU might be reading data while the CPU is updating it, which can cause incorrect results or performance degradation. - By using triple buffering, the CPU and GPU can operate asynchronously, preventing conflicts while ensuring data consistency and improving memory efficiency.

Advantages

- Parallel Execution: Triple buffering allows the CPU and GPU to operate in parallel without blocking each other during read/write operations.

- Higher Memory Throughput: By cycling through multiple buffers, the system reduces stalls caused by synchronization, resulting in better performance.

- Improved Rendering Efficiency: This technique is especially beneficial in rendering pipelines and real-time graphics, where uniform data is frequently updated.